Balancing Speed and Reliability in SPI Bus Communication

Engineers often face the challenge of finding the right balance between speed and reliability when configuring spi communica

Engineers often face the challenge of finding the right balance between speed and reliability when configuring spi communication in electronic devices. For instance, increasing spi bus speed can boost performance in integrated circuits, but it may also introduce instability. Understanding the specific requirements of each spi device and the protocol’s limitations proves essential. Poor spi configuration can lead to serious problems, especially in complex systems. Common causes of data loss or instability include:

- Bus contention from scheduler or FreeRTOS interrupts, which can block DMA operations and cause FIFO overflow.

- FIFO overflow during spi transfers, resulting in lost data.

- Task scheduling conflicts, disrupting the flow of spi data.

Careful attention to these factors helps prevent errors and ensures stable spi operation in modern electronics.

Key Takeaways

- Understand the balance between speed and reliability in SPI communication. Prioritize reliability for sensitive data and speed for real-time applications.

- Optimize SPI bus speed by adjusting clock settings like CPOL and CPHA. Proper configuration reduces errors and enhances data transfer efficiency.

- Maintain signal integrity by using short traces and proper PCB design. This prevents data loss and ensures reliable communication at high speeds.

- Implement error detection routines to catch data transfer issues early. This step is crucial for maintaining system reliability in embedded applications.

- Regularly test SPI performance under real conditions. Use tools like oscilloscopes to monitor signals and troubleshoot potential problems.

SPI Communication Basics

What Is SPI?

SPI stands for Serial Peripheral Interface. Engineers use spi to connect electronic components and integrated circuits. This protocol helps devices exchange data quickly and reliably. SPI uses a simple wiring system with four main signals: clock, master output/slave input, master input/slave output, and chip select. Each signal plays a role in moving data between devices.

SPI has several features that make it different from other serial protocols:

- Synchronous Nature: SPI uses a shared clock signal. Devices do not need to guess when data arrives. The clock keeps everything in sync.

- Full-Duplex Capability: SPI can send and receive data at the same time. This makes communication faster and more efficient.

- Master-Slave Configuration: One device acts as the master. It controls the clock and decides when to talk to each slave device. Multiple slaves can connect, but only one responds at a time.

The master-slave setup in spi communication helps prevent errors. The master device controls which slave talks and when. This design reduces data conflicts and keeps transfers reliable. The master also sends the clock signal, so every device stays in sync. Engineers rely on this structure for real-time data exchange in integrated circuits.

Common Applications

SPI appears in many electronic systems. Engineers use spi to link microcontrollers with sensors, displays, and memory chips. SPI works well in integrated circuits where speed and reliability matter.

Some common uses include:

- Connecting microcontrollers to flash memory for fast data storage.

- Sending commands from a processor to an LCD or OLED display.

- Reading sensor data in industrial control systems.

- Communicating with digital-to-analog converters in audio equipment.

- Linking multiple integrated circuits in embedded systems.

SPI supports high-speed data transfer. It works in devices that need quick responses, such as touchscreens and real-time monitoring systems. Engineers choose spi for its simple wiring and strong performance in electronic components.

SPI Bus Speed Factors

Clock Rate Impact

The clock rate in spi communication sets the pace for data transfer between electronic components. When engineers increase spi bus speed, they boost data throughput. This means more information moves between devices in less time. Faster spi bus speed also reduces latency, which helps microcontrollers respond quickly to sensor data or display updates. In embedded systems, a higher clock rate can improve real-time performance and make high-speed data transfer possible.

- Higher clock speeds improve data transfer rates.

- Increased clock rates can lead to signal integrity issues.

- Balancing clock speed with power consumption is essential.

Most spi devices do not follow a single standard for clock speed. Instead, the maximum spi bus speed depends on the system clock and the capabilities of each device. For many integrated circuits, the maximum spi clock frequency is half of the system clock, but it cannot exceed 12.5 MHz. In industrial and consumer electronics, typical spi bus speeds often reach up to 50 MHz, but actual speeds depend on the hardware and application.

Increasing the spi clock rate enhances data throughput by allowing faster data processing, which leads to improved real-time response in communication protocols. This results in quicker and more precise data exchange, thereby reducing latency in microcontroller applications.

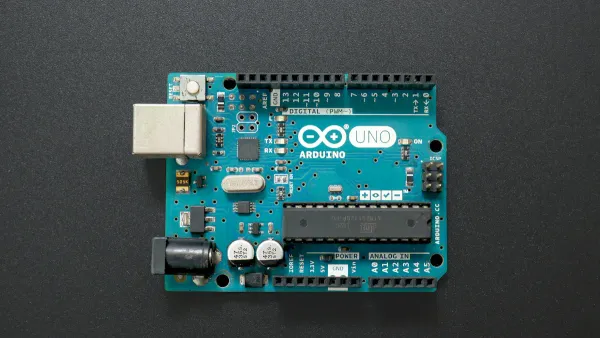

The esp32 microcontroller, for example, supports a wide range of spi bus speeds. Engineers can select the best speed for their application, balancing the need for efficient data transfer with the risk of errors. When using dma or spi dma, higher spi bus speed can help achieve efficient data transfer, but only if the hardware supports it.

Signal Integrity

Signal integrity becomes more important as spi bus speed increases. At higher data transmission speeds, electronic signals can lose their shape. This can cause errors in data transfer between integrated circuits. Factors like rise and fall times, trace lengths, and termination resistors all affect signal quality.

- Signal integrity is essential for spi bus performance, particularly at higher clock rates.

- Rise and fall times, trace lengths, and termination resistors significantly influence signal quality.

- At frequencies above 100 MHz, the relationship between rise time and frequency becomes critical to avoid data loss.

- Proper PCB layout techniques, such as minimizing vias and using appropriate resistors, can help reduce issues like ringing and reflections.

Engineers must design printed circuit boards (PCBs) with care. They should keep spi traces short and avoid unnecessary bends. Using the right resistors helps prevent reflections that can corrupt data. The esp32, like many microcontrollers, benefits from careful PCB design to maintain reliable spi communication at high speeds.

| Hardware Factor | Influence on SPI Bus Speed and Reliability |

|---|---|

| Voltage Levels | Operates at 3.3V or 5V for reliable data exchange |

| Word Length | Adjustable to meet specific performance needs |

| Flow Control | Can be tailored to enhance communication efficiency |

These hardware factors play a key role in maintaining signal integrity and ensuring reliable spi bus speed in embedded systems.

Device Compatibility

Connecting multiple devices to a single spi bus can create compatibility challenges. Each device may have different requirements for spi bus speed, voltage levels, or timing. Some devices ignore the clock and data lines when not selected, but others may cause confusion if not properly managed. Engineers often use external gating or hardware inverters to unify spi setups and prevent conflicts.

- Conflicting spi bus settings can lead to issues.

- Different clock speeds (such as 1 Hz vs. 2 Hz) can cause synchronization problems.

- MOSI and SCK signals can be connected in parallel to multiple devices.

- MISO lines should be tri-stated when devices are not selected.

- Only one device should be activated at a time using its select line.

The esp32 supports multiple spi devices, but engineers must ensure that only one device communicates at a time. This prevents data loss and keeps the spi bus stable. When using dma or direct memory access, engineers must also consider how task scheduling and interrupts affect spi bus speed and reliability.

Timing boundaries, such as setup and hold times, are critical for reliable spi communication. If signals do not meet these timing requirements, data errors can occur. The table below shows typical timing boundaries for spi communication:

| Symbol | Description | Min | Max | Unit |

|---|---|---|---|---|

| Tsu | SPI Master-in slave-out (MISO) setup time | 8.35 | — | ns |

| Th | SPI MISO hold time | 1 | — | ns |

| Ts | MOSI Setup time | 5 | — | ns |

| Th | MOSI Hold time | 5 | — | ns |

The esp32 and other microcontrollers rely on these timing boundaries to ensure reliable high-speed communication. Engineers must check that all devices on the spi bus meet these requirements, especially when using spi dma for efficient data transfer in embedded systems.

Speed vs. Reliability Trade-Offs

Risks of High Speed

Engineers often want to increase spi bus speed to improve data transfer rates in embedded systems. However, running spi at maximum speed can create several problems for electronic components and integrated circuits:

- Latency may increase if the spi bus handles many small transactions. For example, sending only 1 byte at a time can drop the effective data transfer rate from 1Mbps to just 3.95kbps.

- Signal integrity can suffer over longer distances or with poor wiring, leading to data errors.

- Transaction size limits can reduce throughput and cause data integrity issues.

- Devices may not keep up with the fast clock, especially if they do not support high-performance applications.

The esp32 microcontroller supports a wide range of spi speeds, but engineers must consider these risks. Using dma or spi dma can help with efficient data transfer, but only if the hardware and wiring support high speeds. Direct memory access allows the esp32 to move data quickly, but signal quality must remain high for reliable operation.

Reliability Issues

Reliability problems often appear when spi bus speed increases. These issues can affect the performance of embedded systems and cause data loss. The table below shows some common faults in spi communication:

| Fault Description | Cause | Recommended Resolution |

|---|---|---|

| Number of clock pulses not a multiple of 16 | Noise coupling to nCS pin or CLK pin | Add or increase RC filtering on SPI input pins |

| Wrong SPI CRC written | Occurs during Config mode | N/A |

| Invalid SPI frame received | MCU logic error | N/A |

Other reliability issues include:

- Ground arrangement problems can distort spi signals.

- Improper probing techniques may cause ringing, which can look like a failure but may not be the root cause.

- Devices like the esp32 need careful integration with other components to avoid these problems.

Engineers often use dma to reduce cpu load, but they must check for errors caused by noise or poor wiring. The esp32 and similar microcontrollers rely on clean signals for accurate data transfer.

When to Prioritize Each

Choosing between speed and reliability depends on the needs of the device and the application. In high-performance applications, engineers may push the spi bus to its limits to achieve fast data transfer. The esp32 can handle high speeds with dma, making it suitable for fast communication protocols. However, if the system requires stable operation, reliability should come first.

- Engineers should prioritize reliability when working with sensitive data or long spi traces.

- Speed becomes more important in applications that demand quick responses, such as real-time displays or fast sensors.

- The esp32 offers flexibility, allowing engineers to adjust spi settings for the best balance.

Tip: Always test spi bus performance under real conditions. Use proper wiring and check for errors, especially when using dma or direct memory access in embedded systems.

Optimizing SPI Bus Speed

Clock Settings

Engineers often adjust clock settings to optimize spi bus speed in electronic components and integrated circuits. The clock signal, known as SCLK, provides timing and synchronization for spi communication. Two important settings, clock polarity (CPOL) and clock phase (CPHA), determine the idle state of the clock and the timing of data transfer. By configuring CPOL and CPHA, engineers can ensure that data is sampled and transmitted at the right moments, which reduces the risk of errors.

- The SCLK signal keeps spi devices in sync during data transfer.

- CPOL and CPHA settings influence when data is read and written.

- Proper adjustment of these settings improves both speed and reliability.

The esp32 microcontroller allows flexible configuration of spi clock settings. Engineers can select the optimal clock frequency for their application, balancing fast data transfer with reliable operation. When using dma or spi dma, choosing the correct clock settings becomes even more important. High clock speeds can boost performance, but only if the hardware supports clean signal transmission.

Tip: Always test different CPOL and CPHA combinations with your spi devices. This helps identify the best settings for error-free data transfer in embedded systems.

Signal Quality

Signal quality plays a key role in spi communication, especially at higher speeds. Poor signal integrity can lead to data errors and reduce the reliability of integrated circuits. Engineers use several best practices to maintain strong signal quality in spi buses.

- Choose PCB materials with a low dielectric constant for high-speed designs. This improves signal integrity in electronic components.

- Calculate trace width and spacing accurately to maintain impedance and reduce signal loss.

- Maintain a continuous ground plane to control impedance and minimize electromagnetic interference.

- Keep traces short and avoid sharp bends to prevent signal degradation.

- Route differential pairs correctly to maintain timing and reduce errors.

- Avoid crossing split planes to prevent impedance spikes.

- Use vias sparingly to minimize inductance and capacitance effects.

- Separate high-speed and low-speed signals to reduce crosstalk.

Wiring techniques also affect spi signal quality. Engineers minimize the length of connections between devices to reduce delay and signal degradation. Pull-up or pull-down resistors on Chip Select lines prevent floating states, which can cause communication problems. All devices should share a common ground to avoid issues in embedded systems.

| Wiring Technique | Benefit for SPI Bus |

|---|---|

| Proper termination | Prevents signal reflections |

| Short connections | Reduces signal degradation |

| Common ground | Improves communication |

| Pull-up/down resistors on CS | Prevents floating states |

The esp32 benefits from these practices, especially when using dma for fast data transfer. Clean signals help maintain reliable spi communication protocols in electronic components.

Error Detection

Error detection is vital for reliable spi communication in integrated circuits. Unlike some other communication protocols, spi does not include built-in error detection. The responsibility for ensuring data integrity falls on the application layer or additional hardware. If engineers do not implement effective error checking, the system may become vulnerable to data loss or corruption.

Engineers often use software routines to check for errors during data transfer. For example, they may verify the number of clock pulses or use checksums to confirm that data arrived correctly. In embedded systems, the esp32 can run error detection routines alongside dma operations to catch problems early.

Note: Always include error detection in spi applications. This helps maintain system reliability and prevents undetected faults in electronic components.

Power Consumption Considerations

Power consumption changes as spi bus speed increases, especially in battery-powered devices. Higher spi bus speeds can raise power usage because the system must drive capacitive loads and switch signals more often. However, operating at higher speeds allows for longer quiescent periods, which can reduce overall power consumption.

- Faster spi speeds mean the device spends less time transferring data and more time idle.

- For example, a system sampling at 100 kSPS with a 30 MHz SCLK is quiescent 94.67% of the time, compared to 84% with a 10 MHz SCLK.

- This results in significant power savings for embedded systems using the esp32.

Engineers must balance the need for fast data transfer with the impact on battery life. When using dma or spi dma, they should monitor power usage and adjust spi bus speed to match the requirements of their electronic components.

⚡ Tip: Test power consumption at different spi bus speeds. This helps optimize battery life and ensures efficient operation in embedded systems.

Real-World Examples

High-Speed Systems

Engineers use spi in high-speed systems to connect electronic components and integrated circuits. The esp32 microcontroller often manages fast data exchange between sensor hubs and memory chips. In complex battery systems, spi enables rapid communication for monitoring and control. Industrial automation relies on spi for real-time applications, where multiple devices must work together without delay. The esp32 supports spi dma, which allows efficient data transfer and reduces cpu load. Proper board design helps prevent cross talk and noise, keeping signals clear. Engineers use oscilloscopes and logic analyzers to check spi signals and troubleshoot problems. The table below shows how different application areas benefit from balancing speed and reliability:

| Application Area | Key Benefits |

|---|---|

| Complex Battery Systems | High-speed data transfer for rapid communication |

| Industrial Automation | Real-time applications with multiple device connections |

| IoT Systems | Flexibility and scalability in communication |

Consumer Devices

Consumer devices like smart watches, fitness trackers, and home automation controllers use spi for fast and reliable communication. The esp32 often connects to displays, sensors, and storage chips using spi. Embedded systems in cars use spi to support safety and comfort features. Engine control units depend on spi for consistent performance. Engineers must initialize spi correctly to avoid floating voltage levels during startup. Weak pull-up resistors on Chip Select lines help keep devices de-selected until the microcontroller is ready. Debugging tools reveal misconfigured phase and polarity settings, which engineers fix by checking datasheets and using oscilloscopes. The table below highlights key benefits in embedded designs and automotive systems:

| Application Area | Key Benefits |

|---|---|

| Embedded Designs | Reliable and adaptable for high-speed communication |

| Automotive Systems | Low latency and consistent performance |

Lessons Learned

Engineers have learned several important lessons from spi bus misconfiguration in electronic components and integrated circuits. They adjust clock speed to balance noise and performance. Pull-up or pull-down resistors prevent floating states, especially on Chip Select lines. Level shifters match voltage levels between master and slave devices, avoiding signal errors. Engineers set the spi clock speed to match the slowest device on the bus. Shielded cables and controlled impedance traces improve signal integrity. Troubleshooting steps include checking physical connections, using logic analyzers, and monitoring voltage with multimeters. Debugging software helps find configuration errors. The table below lists common troubleshooting steps:

| Step | Description |

|---|---|

| 1 | Check physical connections between master and slave devices, ensuring all wires are secure and correctly connected. |

| 2 | Use a logic analyzer to capture and analyze digital signals on the spi bus, identifying errors or anomalies. |

| 3 | Utilize a multimeter to measure voltage and resistance, checking for short circuits or voltage drops. |

| 4 | Employ debugging software to monitor spi communication, helping to identify configuration errors or protocol violations. |

Note: Engineers recommend setting the maximum spi clock frequency based on the slowest signal. For example, they may choose 2 MHz instead of 2.5 MHz to ensure data integrity in embedded systems using the esp32 and dma.

Balancing speed and reliability in spi bus communication requires careful attention to environmental conditions, application needs, and protocol features. Engineers working with electronic components and integrated circuits should test and validate their systems regularly to ensure long-term reliability, especially when handling unexpected events or high-speed data transfers. For those interested in advanced techniques, several resources offer deeper insights into spi configuration and best practices:

- SPI Tutorial: A comprehensive guide on configurations and transactions.

- Better SPI Bus Design: Tips for setting up reliable networks.

FAQ

What is the maximum safe SPI bus speed for most integrated circuits?

Most integrated circuits support SPI bus speeds up to 50 MHz. Engineers should check the datasheet for each device before setting the clock rate. Exceeding the recommended speed can cause data errors or unstable communication.

How can engineers improve SPI reliability in electronic components?

Engineers use short traces, proper termination, and pull-up resistors to improve SPI reliability. They also test different clock settings and monitor signal quality with oscilloscopes. These steps help prevent data loss and communication faults.

Why do some SPI devices require specific clock polarity and phase settings?

Each SPI device may use different clock polarity (CPOL) and phase (CPHA) settings. These settings control when data is sampled and transmitted. Matching these values ensures correct communication between integrated circuits.

Can SPI communication support multiple devices on one bus?

SPI supports multiple devices using separate chip select lines. Only one device communicates at a time. Engineers must ensure that unused devices do not interfere with the bus by tri-stating their MISO lines.

What tools help engineers troubleshoot SPI bus problems?

Engineers use logic analyzers, oscilloscopes, and multimeters to find SPI bus problems. These tools help check signal timing, voltage levels, and data integrity in electronic components and integrated circuits.