Achieving Higher MTBF Through HiSilicon AI

HiSilicon AI SoCs increase system mean time between failures (MTBF). They provide a foundation for reliable AI systems. A sy

HiSilicon AI SoCs increase system mean time between failures (MTBF). They provide a foundation for reliable AI systems. A system failure carries a high cost; a high frequency of failures lowers the system MTBF. Engineers design robust systems to reduce this frequency and cost. Designing robust systems for higher reliability hinges on a complete system design approach. This approach lowers failure frequency and cost, improving the overall MTBF. The system cost and frequency of failures define the MTBF.

Three Pillars of System Reliability A robust system design achieves higher MTBF and reliability by focusing on three core areas:

- Hardware-level reliability

- Thermal management design

- Software and system resilience

Key Takeaways

- HiSilicon AI chips make systems more reliable. They help systems last longer and break down less often.

- Good hardware, like ECC memory and stable power, makes systems strong. This prevents many common problems.

- Keeping chips cool is very important. HiSilicon designs chips that use less power and have smart ways to manage heat.

- Software must also be strong for a reliable system. HiSilicon uses secure startup and watchdog timers to fix software issues quickly.

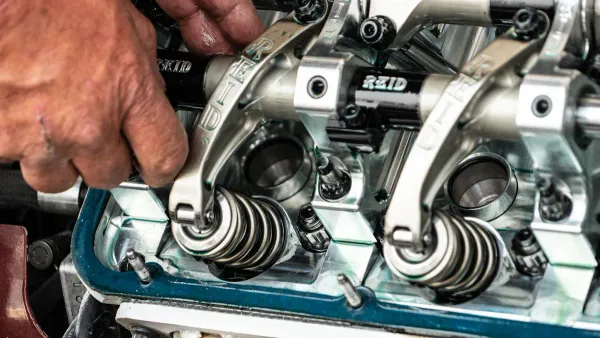

HARDWARE FOUNDATIONS FOR SYSTEM RELIABILITY

Hardware forms the bedrock of system reliability. A system's MTBF depends heavily on the quality of its underlying components. Continuous AI workloads create intense heat and voltage stress. This stress accelerates the degradation of silicon, increasing the failure rate. HiSilicon addresses this challenge at the source. The company's high-quality silicon and advanced manufacturing processes result in a lower intrinsic failure rate, providing a robust foundation for system longevity. This initial quality reduces the overall cost of failure over the product's life.

ECC MEMORY AND DATA INTEGRITY

Silent data corruption is a frequent cause of system failure. It can be difficult to diagnose. This issue directly lowers the practical MTBF of a system. HiSilicon SoCs integrate Error-Correcting Code (ECC) memory to improve data integrity and system stability.

ECC memory automatically detects and corrects single-bit errors in real-time. This hardware redundancy prevents memory-related crashes and ensures the accuracy of AI computations. It protects critical components like Static Random-Access Memories (SRAMs) from contributing to a higher failure frequency. This feature is vital for maintaining performance and reliability.

INTEGRATED POWER MANAGEMENT

Power fluctuations are a significant source of component stress. They can lead to a higher frequency of hardware failure and a lower MTBF. HiSilicon SoCs feature an integrated Power Management IC (PMIC). This design provides clean and stable power rails to all parts of the chip. Even under heavy AI processing loads, the PMIC prevents voltage droops. This stability reduces stress on the silicon, lowers the component failure rates, and increases the overall system reliability. A stable power design is a low-cost way to achieve a higher MTBF.

SILICON AND MANUFACTURING QUALITY

The ultimate reliability of a system begins with the quality of its smallest parts. HiSilicon's commitment to quality includes rigorous testing and superior materials. The design uses high-quality quartz crystals for the crystal oscillator, ensuring excellent frequency stability. This attention to detail minimizes failure mechanisms from the start. The manufacturing process includes extensive reliability testing and environmental testing. This testing validates the hardware redundancy and performance of every chip. This focus on quality ensures a predictable Failure in Time (FIT) rate, contributing to a more dependable system and a higher MTBF.

DESIGNING ROBUST SYSTEMS WITH THERMAL MANAGEMENT

Excessive heat is a primary driver of electronic failure, directly increasing the failure rate and lowering a system's MTBF. Designing robust systems therefore requires a comprehensive thermal management strategy. The relationship between heat and reliability is well-documented.

A useful rule of thumb, supported by the Arrhenius equation, states that for every 10°C increase in operating temperature, the lifespan of an electronic component can be cut in half. This makes thermal control a critical factor in achieving a high MTBF.

HiSilicon addresses this challenge through a multi-layered design approach that combines active management, efficient architecture, and practical engineering guidance. This approach lowers the total cost of ownership by reducing the frequency of thermal-related failures.

THERMAL SENSORS AND DFS

HiSilicon AI SoCs embed multiple thermal sensors directly onto the die. These sensors provide real-time temperature data, allowing the system to react intelligently to changing thermal loads. This data feeds into the Dynamic Frequency Scaling (DFS) mechanism. DFS automatically adjusts the chip's operating frequency and voltage based on the current workload and temperature. This active management prevents thermal runaway during intense AI processing, ensuring both performance and stability. This process maintains excellent frequency stability across the system, contributing to higher reliability.

LOW-POWER ARCHITECTURE

A core principle of HiSilicon's design philosophy is power efficiency. A low-power architecture inherently generates less heat, which reduces thermal stress and lowers the long-term failure rate. This efficient design directly translates to a lower operational cost and improved system reliability. Compared to competitors, HiSilicon's design demonstrates superior performance per watt, a key metric for robust systems operating in thermally constrained environments.

| SoC | Load Condition | Power Consumption (W) |

|---|---|---|

| HiSilicon Kirin 9000W | Geekbench 5.5 (150cd *100%) | 5.62 (min) - 10.1 (max) |

| Apple M2 | Geekbench 5.5 | 6.86 (min) - 9.71 (max) |

This efficiency is fundamental to building robust systems with a predictable MTBF. The lower power frequency reduces the overall system cost.

REFERENCE DESIGNS FOR HEAT DISSIPATION

HiSilicon extends its commitment to reliability beyond the chip itself by providing engineers with detailed reference designs. These guides offer proven layouts for passive cooling solutions, such as heat sinks and chassis ventilation. This guidance simplifies the task of designing robust systems, ensuring that the thermal performance of the final product meets reliability targets. This holistic system design approach considers every component, including the stability of the crystal oscillator, which relies on high-quality quartz crystals. The use of quality components like quartz crystals ensures high frequency stability, which is essential for system accuracy and performance. This comprehensive design support reduces development cost and time, helping teams achieve a higher MTBF more efficiently.

SOFTWARE STRATEGIES FOR A HIGHER MTBF

Robust hardware requires resilient software to achieve high reliability. A system can fail even with perfect hardware. Software faults increase the failure frequency and the total cost of ownership. A comprehensive software design strategy is essential for a higher MTBF. It focuses on integrity, recovery, and stability. This approach reduces the overall system failure rate.

SECURE BOOT AND FIRMWARE INTEGRITY

System stability begins the moment a device powers on. HiSilicon SoCs implement a secure boot process. This hardware-level redundancy ensures the system only loads authenticated firmware. It prevents malicious code from compromising the system, which is a primary step toward software reliability. This design provides a trusted foundation for all operations. Rigorous testing of all software components further reduces the frequency of defects.

A 1985 study by computer scientist Jim Gray found that software and operations were the primary drivers of system failure. This insight remains true today. Addressing software issues is key to increasing MTBF, even when hardware functions correctly.

This focus on software quality minimizes the operational cost and failure frequency over the product's life.

WATCHDOG TIMERS FOR RECOVERY

Software can sometimes freeze or enter an unresponsive state. A hardware watchdog timer provides a critical layer of redundancy to handle such events. This timer is an independent counter on the chip. The system software must periodically reset this counter to signal normal operation.

- If the software hangs, it fails to reset the timer.

- The counter reaches zero.

- The hardware automatically triggers a system reboot.

This fail-safe mechanism returns the system to a known-good state without human intervention. This automatic recovery improves system availability and performance. It directly contributes to a higher MTBF by reducing downtime from software hangs. This low-cost feature greatly improves system reliability.

STABLE DRIVERS AND SDK SUPPORT

Device drivers are a common source of system instability. Poorly written drivers can cause hangs, data loss, or complete system failure. This directly lowers the practical MTBF. HiSilicon mitigates this risk by providing a high-quality Software Development Kit (SDK). This kit includes stable, well-tested drivers optimized for the hardware. This support ensures high performance and accuracy. A good driver design reduces the frequency of software-related problems. This lowers the support cost and improves the end-user experience. This commitment to software stability is vital for building a dependable system with predictable reliability.

Engineers achieve a higher system MTBF by focusing on three core areas. These are hardware reliability, thermal design, and software stability. Designing robust systems this way lowers the failure frequency and total system cost. Engineers use HiSilicon AI SoCs to build robust systems and reliable AI systems. This system design improves overall system reliability. It reduces the failure frequency and operational cost. A lower failure frequency reduces the system cost, improving the MTBF. Designing robust systems with high reliability lowers the failure frequency and total cost, leading to a predictable MTBF. Engineers reduce the failure frequency for a higher MTBF.

FAQ

How does ECC memory improve MTBF?

ECC memory detects and corrects single-bit data errors in real-time. This hardware feature prevents system crashes caused by memory corruption. It ensures data integrity and stable performance, directly increasing the system's MTBF.

Why is thermal management important for reliability?

A good thermal design is critical for system longevity.

- High temperatures accelerate component degradation.

- Effective thermal management keeps the SoC cool.

- This process reduces stress, improves long-term performance, and raises the MTBF.

What role does a watchdog timer play?

A watchdog timer acts as a fail-safe for software freezes. It automatically reboots the system if the software becomes unresponsive. This automated recovery mechanism minimizes downtime and increases overall system availability.

How does silicon quality affect system performance?

High-quality silicon and rigorous testing reduce the intrinsic failure rate from the start. A stable crystal oscillator, using high-quality quartz crystals, ensures excellent system performance. This focus on quality provides a reliable foundation for the entire product.